This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

# A Class of SEC-DED-DAEC Codes Derived From Orthogonal Latin Square Codes

Pedro Reviriego, Salvatore Pontarelli, Adrian Evans, and Juan Antonio Maestro

Abstract-Radiation-induced soft errors are a major reliability concern for memories. To ensure that memory contents are not corrupted, single error correction double error detection (SEC-DED) codes are commonly used, however, in advanced technology nodes, soft errors frequently affect more than one memory bit. Since SEC-DED codes cannot correct multiple errors, they are often combined with interleaving. Interleaving, however, impacts memory design and performance and cannot always be used in small memories. This limitation has spurred interest in codes that can correct adjacent bit errors. In particular, several SEC-DED double adjacent error correction (SEC-DED-DAEC) codes have recently been proposed. Implementing DAEC has a cost as it impacts the decoder complexity and delay. Another issue is that most of the new SEC-DED-DAEC codes miscorrect some double nonadjacent bit errors. In this brief, a new class of SEC-DED-DAEC codes is derived from orthogonal latin squares codes. The new codes significantly reduce the decoding complexity and delay. In addition, the codes do not miscorrect any double nonadjacent bit errors. The main disadvantage of the new codes is that they require a larger number of parity check bits. Therefore, they can be useful when decoding delay or complexity is critical or when miscorrection of double nonadjacent bit errors is not acceptable. The proposed codes have been implemented in Hardware Description Language and compared with some of the existing SEC-DED-DAEC codes. The results confirm the reduction in decoder delay.

*Index Terms*—Double adjacent error correction (DAEC), error correction codes, memory, orthogonal latin squares (OLS), single error correction double error detection (SEC-DED).

## I. INTRODUCTION

Radiation-induced soft errors are a major concern for memory reliability [1]. To protect memories, error correction codes are commonly used [2]. Traditionally, single error correction double error detection (SEC-DED) codes have been used [3]. A SEC-DED code has a minimum Hamming distance of four and is able to correct single bit errors and detect double errors without miscorrection. This is important to avoid silent data corruption. SEC-DED codes are sufficient when errors affect only one bit, however, the percentage of soft errors affecting more than a single bit is increasing as technology scales [4]. For memories implemented in 40 nm and below, multiple bit errors are a significant percentage of errors and thus SEC-DED codes alone are no longer sufficient to protect memories. One option is to combine SEC-DED codes with interleaving [5]. Interleaving, places the bits that belong to the same logical word physically apart. As the errors caused by a radiation particle hit are physically close [6], this ensures that the errors affect at most one bit per logical word. Interleaving has an impact on the memory design. The routing is more complex and area and power consumption are increased. In addition, interleaving cannot always be used in small memories

Manuscript received August 6, 2013; revised January 29, 2014; accepted April 16, 2014. This work was supported in part by the Spanish Ministry of Science and Education under Grant AYA2009-13300-C03 and in part by the framework of COST ICT Action 1103 through the Manufacturable and Dependable Multicore Architectures at Nanoscale.

P. Reviriego and J. A. Maestro are with the Universidad Antonio de Nebrija, Madrid E-28040, Spain (e-mail: previrie@nebrija.es; jmaestro@nebrija.es).

S. Pontarelli is with the University of Rome "Tor Vergata," Rome 00133, Italy (e-mail: pontarelli@ing.uniroma2.it).

A. Evans is with Iroc Technologies, Grenoble 38000, France (e-mail: adrian.evans@iroctech.com).

Digital Object Identifier 10.1109/TVLSI.2014.2319291

Recomputed 2t check bits for bit d<sub>i</sub> Majority circuit d<sub>i</sub> decoded d<sub>i</sub> bit

Fig. 1. Illustration of OS-MLD decoding for OLS codes.

or register files nor can be practically applied to content addressable memories [7]. Another alternative is to use error correction codes that can correct adjacent bits. In many cases, directly adjacent bits account for over 90% of the observed multiple bit errors. Several codes have been recently proposed to this end. For example, a code that can correct double and triple adjacent errors for words of 16 bit was presented in [8]. In [9], a technique to design SEC-DED double adjacent error correction (SEC-DED-DAEC) codes was introduced. The extension of SEC-DED-DAEC codes to also detect larger burst errors has also been recently considered in [10]. One issue with those SEC-DED-DAEC codes is that they can miscorrect some double nonadjacent bit errors. The reduction of the miscorrection probability has been considered in [9] and [11]. In [9], the algorithm tries to minimize the number of 4 cycles. In [12], it was shown that miscorrection can be avoided for the most common error patterns and in some cases for all patterns at the cost of adding additional parity check bits. Another issue with SEC-DED-DAEC codes is that their decoding complexity and latency are larger than those of SEC-DED codes. This limits their use when speed is a critical factor. This issue was addressed in [13] where codes that can correct adjacent errors and have simple and fast decoders were presented. The main limitation for these codes is that they require a number of parity check bits equal to the number of data bits. The use of more advanced codes such as difference set and orthogonal latin squares (OLS) codes to correct adjacent errors has also been considered in [14] and [15]. Those codes are one-step majority logic decodable (OS-MLD) and therefore, can be decoded with low latency. They also support the correction of multiple nonadjacent bit errors, a protection level that may be excessive in some memory applications.

In this brief, a new class of SEC-DED-DAEC codes is presented. The proposed codes are derived from OLS codes. They require fewer parity check bits than double error correction (DEC) OLS codes and are simpler to decode. Compared with existing SEC-DED-DAEC codes, the new codes have two main advantages: first, there are no miscorrections for double nonadjacent errors and second, the decoding is much simpler and faster. The main drawback for the proposed codes is that they require more parity check bits than existing SEC-DED-DAEC codes. Therefore, the proposed codes can be useful to protect memories in which decoding latency is critical or miscorrections cannot be tolerated. The rest of this brief is organized as follows. In Section II, OLS codes are briefly presented. In Section III, the proposed SEC-DED-DAEC codes are derived and their error correction capabilities are discussed. Section IV presents an evaluation of the new codes focusing on decoding latency and

1063-8210 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

| $\mathbf{M}_1$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                | 0<br>0<br>0                                   |

|----------------|-------------------------------------------------------------------------------------|-----------------------------------------------|

|                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                               | 0                                             |

|                |                                                                                     | 0                                             |

| $M_2$          | 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0               | 0                                             |

|                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                               | $\begin{bmatrix} 0 \\ 0 \end{bmatrix} I_{4m}$ |

|                | $\begin{array}{c} 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & 1 & 0 & 0$                        | 0                                             |

| $M_3$          |                                                                                     | 0                                             |

|                | 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 0 0 0 0                                             | 0                                             |

|                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                | 0                                             |

| $M_4$          | $\begin{smallmatrix} 0 & 1 & 0 & 0 & 0 & 0 & 1 & 0 & 0 & 1 & 0 & 1 & 0 & 1 & 0 & 0$ | 0                                             |

|                |                                                                                     | 1                                             |

Fig. 2. Parity check matrix H for the OLS code with k = 16 and t = 2.

circuit area. Finally, the conclusion and ideas for future work are discussed in Section V.

## II. OLS CODES

OLS codes were introduced decades ago to protect memories [16] and have recently been proposed to protect caches [17] and interconnects [18].

The block sizes for OLS codes are  $k = m^2$  data bits and 2tm parity bits. Where t is the number of errors that the code can correct and m is an integer. For memories, the word sizes are typically a power of two and therefore m is commonly also power of two. The main advantage of OLS codes is that their decoding is simple and fast. This is because, as mentioned in the introduction, OLS codes can be decoded using OS-MLD. In OS-MLD, each bit is decoded by simply taking the majority value on the set of the recomputed parity check equations (or syndrome bits) in which it participates [19]. This is shown in Fig. 1 for a given data bit  $d_i$ . The idea behind OS-MLD is that when an error occurs in bit  $d_i$ , the recomputed parity checks in which it participates will take a value of one unless there are errors in other bits. Therefore, a majority of ones in those recomputed checks is an indication that the bit is in error and therefore needs to be corrected. If the code is such that two bits share at most one parity check, then t-1 errors on other bits will not affect the majority of the 2t vote and therefore, the error will be corrected. Only a few codes have this property and can be decoded using OS-MLD [19]. This is the case for difference set codes and for OLS codes, as mentioned in the introduction.

- More formally, the construction of OLS codes is such that:

- 1) each data bit participates in exactly 2t parity check bits;

- 2) each other data bit participates in at most one of those parity check bits.

Therefore, for a number of errors t or smaller, when one error affects a given bit, the remaining t - 1 errors can, in the worst case affect t - 1 check bits on which that bit participates. Therefore, still a majority of t + 1 will trigger the correction on the erroneous bit. Conversely, when a given bit is correct, t errors on other bits will not cause miscorrection as a majority of t + 1 is needed. As shown in Fig. 1, the use of OS-MLD enables a simple and fast decoding that is attractive to protect memories when decoding latency is critical. Another characteristic of OLS codes is that they correct only errors on the data bits. No correction is done for the parity bits. This is not an issue as in memories, the goal is to recover the stored data correctly.

As mentioned in the introduction, the proposed codes are derived from DEC OLS codes. These are block linear codes that are defined by their parity generating G and parity check H matrixes [19]. The parity check matrix is used to detect errors by computing the

TABLE I PARAMETERS OF SOME DEC OLS CODES

| k   | n-k | m  |

|-----|-----|----|

| 16  | 16  | 4  |

| 64  | 32  | 8  |

| 256 | 64  | 16 |

syndrome *s* that is obtained by multiplying the stored word by the *H* matrix. The parity check matrix *H* for a DEC OLS code with  $k = m^2$  is constructed as follows:

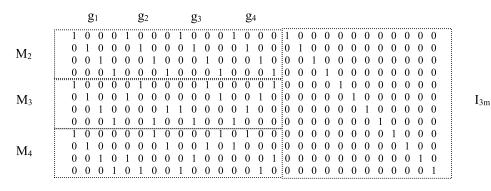

$$H = \begin{bmatrix} M_1 \\ M_2 \\ M_3 \\ I_{4m} \\ M_4 \end{bmatrix} \tag{1}$$

where  $I_{4m}$  is the identity matrix of size 4m and  $M_1, M_2, M_3, M_4$ are matrices with size  $m \times m^2$  derived from OLS of size  $m \times m$ . The weight or the number of ones, of all the columns, in the  $M_i$ matrices must be one. Therefore, the first  $k = m^2$  columns in Hhave a number of ones equal to 2t (four for DEC codes). In addition, any pair of columns has at most a position with a one in common. This as discussed before enables the use of OS-MLD for decoding. As an example, the H matrix for a code with  $k = m^2 = 16$  data bits and 2tm = 16 parity bits that can correct double errors is shown in Fig. 2. The parameters of some DEC OLS codes are summarized in Table I.

### III. PROPOSED SEC-DED-DAEC CODES

The proposed codes are derived from DEC OLS codes. Taking the parity check matrix in (1) as a starting point, the first step is to remove the *m* parity check bits that correspond to one of the  $M_i$ matrices. As an example, consider removing the  $M_1$  matrix from the matrix in Fig. 2 as shown in Fig. 3. The data bits that participated in each of the removed parity check equations will not share any parity check in the reduced matrix. This is a direct consequence from the property of OLS codes that any two data bits share (that is have a one in the same row in the H matrix) at most one parity check bit. This can be clearly observed in Fig. 2. In addition, those groups of m bits are marked as g<sub>1</sub>, g<sub>2</sub>, g<sub>3</sub>, and g<sub>4</sub> in Fig. 3. For example, the first four data bits share the first parity check bit in the  $M_1$  matrix and form the first group  $g_1$ . It can be observed that they do not share any other parity check bits. Therefore, when  $M_1$  is removed they do not share any parity check bit. The same occurs for the other groups of bits  $5-8(g_2), 9-12(g_3), and 13-16(g_4)$ . In the reduced matrix, each data bit participates in three parity checks. Therefore, if a majority vote is used to decode the bits, single and double errors can be corrected.

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

Fig. 3. Reduced parity check matrix H after the removal of  $M_1$ .

Fig. 4. Illustration of the proposed decoder for data bits 1 and 2.

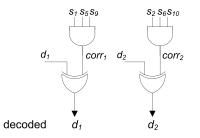

However, double errors can also cause miscorrections on other bits. Therefore, the modified matrix, when a majority vote is used, is only effective in correcting single errors. However, let us consider that instead of a majority vote, the logical AND of the three parity checks is used. In Fig. 4, this is shown for the first two data bits where the  $s_i$  values correspond to bits of the syndrome vector obtained by multiplying the word by the *H* matrix. In this case, the code will obviously not miscorrect when there are two errors. Single errors on data bits will also be corrected. Double errors affecting data bits will also be corrected as long as the data bits do not share any parity check bit.

The two modifications (matrix reduction and voting by unanimity) can now be linked together by noting that errors that affect bits in one group of bits that share a parity check bit in  $M_1$  will now be corrected. For example, an adjacent error in bits 1 and 2 will cause the recomputed parity checks 1, 2, 5, 6, 9, and 10 to give a value of one. The ones on parity checks 1, 5, and 9 will trigger a correction on bit 1 while the ones on parity checks 2, 6, and 10 will trigger a correction on bit 2. This is clearly observed in Fig. 4. In this case, the recomputed parity checks are denoted as  $s_i$  to make clear that they are in fact bits from the syndrome. However, some double adjacent errors may affect bits on different groups. For example, an error on bits 8 and 9 affects a bit in  $g_2$  and another in  $g_3$ . These bits share parity check bit 7 and therefore, will not be corrected as that recomputed parity bit will take a value of zero in the syndrome as it has two bits in error. This effect can be avoided by carefully placing the bits in the memory. For example, the bits within each group can be reordered to ensure that the ones at the borders does not share any parity check bit with the adjacent bit on the other group. Another issue that can occur is that a double adjacent error affects two parity bits and the error is confused with a double nonadjacent error. For example, an error on parity check bits 4 and 5 produces the same syndrome as an error that affects data bit 16 and parity check bit 11. This can lead to silent data corruption leaving an error on data bit 16 undetected. However, this issue can also be solved by carefully placing the bits into the memory.

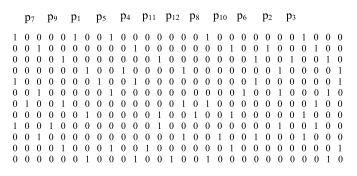

Fig. 5. Reduced parity check matrix H after the removal of  $M_1$  with the proposed bit placement.

Fig. 6. Detection of double uncorrectable errors in the proposed scheme.

The proposed bit placement is as follows: 1) ensure that the bits at the borders of the groups do not share any parity check bits and 2) interleave the parity check bits with the data bits so that no double adjacent error affects two parity bits. An example of this bit placement for the code with k = 16 is shown in Fig. 5. The parity bits are marked in the figure and obviously, they can only be placed such that the adjacent columns do not participate in the parity bit. With this bit placement, all double adjacent errors affect at least a data bit and that data bit is corrected.

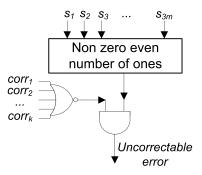

In addition, for nonadjacent errors that affect two bits, if any bit is corrected it means that the error is correctable. When the error affects two data bits, either they are both corrected or there is no correction. Obviously, when the error affects a data bit and a parity bit, if the data bit is corrected the error was correctable. This enables a simple method to detect uncorrectable errors. The proposed scheme to detect the uncorrectable errors is shown in Fig. 6. It is based on detecting a nonzero even number of ones in the syndrome that can only be caused by a multiple bit error and checking if any correction has been made.

TABLE II PARAMETERS OF THE PROPOSED SEC-DED-DAEC CODES

| 1 | k   | n-k | т  |

|---|-----|-----|----|

|   | 16  | 12  | 4  |

|   | 64  | 24  | 8  |

|   | 256 | 48  | 16 |

The proposed scheme can be summarized as follows:

- 1) reduce the H matrix of the DEC OLS code by eliminating  $M_1$ ;

- 2) place the bits in the groups of *m* bits  $g_1, g_2, \ldots, g_m$  such that the bits at the borders of the groups do not share any parity check:

- interleave the parity bits with the data bits such that two adjacent bits never participate in the same parity bit;

- instead of majority voting, decode based on unanimity (three-way AND) to correct errors;

- 5) implement the circuit of Fig. 6 to detect uncorrectable errors.

This scheme can correct all double adjacent errors that affect data bits and detect all noncorrectable double errors. Therefore, the derived codes are SEC-DED-DAEC with no miscorrection. In addition, some double nonadjacent errors are also corrected and the fraction of these errors that can be corrected grows with the block size. The parameters of the derived codes for the block sizes that are commonly of interest for memory protection are summarized on Table II. It can be observed that the number of required parity check bits is significantly higher than traditional SEC-DED-DAEC codes [9] but this is the price to pay for faster decoding and the absence of miscorrections. Miscorrections can also be avoided with a lower number of parity checks bits using the scheme presented in [12]. For example, for k = 64 a SEC-DED-DAEC with no miscorrection required 12 bit compared with the 24 of the proposed codes. In that case, the main benefit of the new codes is the simple and fast decoding. In the next section, the area and delay of the decoder for the proposed codes are compared with that of existing SEC-DED-DAEC codes to put their performance in perspective.

### IV. EVALUATION

For the parameters shown in Table II, the proposed SEC-DED-DAEC extended codes have been implemented in MATLAB where their error correction capabilities were validated for single and double adjacent errors. As the number of combinations of single and double adjacent errors is small (2n - 1), these were tested exhaustively. For the nonadjacent double errors, 100 000 combinations were randomly generated and tested to ensure that the errors were corrected or detected as uncorrectable. The results confirm the theoretical analysis in that the codes are SEC-DED-DAEC with no miscorrection.

The encoders and decoders have also been implemented in Hardware Description Language (HDL) and synthesized for the 45-nm OSU FreePDK Standard Cell library [20] using Synopsys Design Compiler. The synthesizer is configured to optimize the delay. Therefore, the results provide the lowest delay that can be achieved. The reported circuit area could be reduced at the expense of increasing the delay. The area and delay results only for the encoders and decoders are presented in Tables III and IV. As expected, the decoders for the proposed codes are simpler and faster than those of existing SEC-DED-DAEC codes. In particular, the SEC-DED-DAEC codes presented in [12] for k = 16 and for k = 64that avoid miscorrections for double nonadjacent errors that are separated up to a distance of five are used for comparison. The results show that the decoder area is less than one half of that required by the codes in [12] and the delay is also greatly reduced (45% and 50% for k = 16 and k = 64, respectively). The reduction in the encoder delay is also significant: 12% and 24%, respectively. The results

TABLE III Area Estimates (in  $\mu$ m<sup>2</sup>)

|     | Proposed codes |         |         | Proposed codes SEC-DED-DAEC in [12] |         |         | C in [12] |

|-----|----------------|---------|---------|-------------------------------------|---------|---------|-----------|

| k   | n-k            | Encoder | Decoder | n-k                                 | Encoder | Decoder |           |

| 16  | 12             | 158     | 457     | 7                                   | 190     | 1,098   |           |

| 64  | 24             | 831     | 1,976   | 9                                   | 805     | 4,369   |           |

| 256 | 48             | 3,687   | 6,927   | -                                   | -       | -       |           |

TABLE IV Delay Estimates (in Nanoseconds)

|     | Proposed codes |         |         | SEC-DED-DAEC in [12] |         |         |

|-----|----------------|---------|---------|----------------------|---------|---------|

| k   | n-k            | Encoder | Decoder | n-k                  | Encoder | Decoder |

| 16  | 12             | 0.22    | 0.25    | 7                    | 0.25    | 0.47    |

| 64  | 24             | 0.25    | 0.34    | 9                    | 0.33    | 0.69    |

| 256 | 48             | 0.28    | 0.45    | -                    | -       | -       |

confirm that the proposed codes are significantly faster than existing SEC-DED-DAEC alternatives making them attractive for high-speed memories like caches [17]. They also avoid miscorrections for double nonadjacent errors. The price to pay is that the number of parity check bits needed (n - k) is significantly larger than for existing SEC-DED-DAEC codes.

# V. CONCLUSION

In this brief, a new class of SEC-DED-DAEC codes has been presented. The codes are derived from DEC OLS codes and can be decoded with low latency. Another interesting feature is that the codes do not experience miscorrections when double nonadjacent error occurs. This is interesting to minimize silent data corruption. The codes can also correct some nonadjacent double errors. Compared with existing SEC-DED-DAEC codes, they require a larger number of parity check bits, therefore, they are attractive when low latency decoding is a required. The codes have been implemented in HDL and the resulting implementations compared with existing SEC-DED-DAEC codes to put the reductions in decoding latency in perspective.

The ideas used to derive the proposed SEC-DED-DAEC can also be used to derive burst error correction codes from OLS codes that can correct multiple errors. The key observation is that the structure of OLS codes is such that the data bits can be divided in groups of *m* bits that do not share any parity check. Therefore, any error affecting up to 2t-1 bits in one of these groups can be corrected. This can be exploited by carefully placing the data and parity check bits so that, in the best case, up to 2t-1 adjacent bit errors can be corrected. The development of burst error correction codes is an interesting avenue to continue and extend the work presented in this brief.

#### REFERENCES

- [1] R. C. Baumann, "Soft errors in advanced computer systems," *IEEE Des. Test. Comput.*, vol. 22, no. 3, pp. 258–266, May/Jun. 2005.

- [2] C. L. Chen and M. Y. Hsiao, "Error-correcting codes for semiconductor memory applications: A state-of-the-art review," *IBM J. Res. Develop.*, vol. 28, no. 2, pp. 124–134, Mar. 1984.

- [3] M. Y. Hsiao, "A class of optimal minimum odd-weight-column SEC-DED codes," *IBM J. Res. Develop.*, vol. 14, no. 4, pp. 395–301, Jul. 1970.

- [4] E. Ibe, H. Taniguchi, Y. Yahagi, K. Shimbo, and T. Toba, "Impact of scaling on neutron-induced soft error in SRAMs from a 250 nm to a 22 nm design rule," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1527–1538, Jul. 2010.

- [5] P. Reviriego, J. A. Maestro, S. Baeg, S. Wen, and R. Wong, "Protection of memories suffering MCUs through the selection of the optimal interleaving distance," *IEEE Trans. Nucl. Sci.*, vol. 57, no. 4, pp. 2124–2128, Aug. 2010.

- [6] S. Satoh, Y. Tosaka, and S. A. Wender, "Geometric effect of multiple-bit soft errors induced by cosmic ray neutrons on DRAM's," *IEEE Electron Device Lett.*, vol. 21, no. 6, pp. 310–312, Jun. 2000.

- [7] S. Baeg, S. Wen, and R. Wong, "Minimizing soft errors in TCAM devices: A probabilistic approach to determining scrubbing intervals," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 4, pp. 814–822, Apr. 2010.

- [8] X. She, N. Li, and D. W. Jensen, "SEU tolerant memory using error correction code," *IEEE Trans. Nucl. Sci.*, vol. 59, no. 1, pp. 205–210, Feb. 2012.

- [9] A. Dutta and N. A. Touba, "Multiple bit upset tolerant memory using a selective cycle avoidance based SEC-DED-DAEC code," in *Proc. 25th IEEE VLSI Test Symp.*, May 2007, pp. 349–354.

- [10] A. Neale and M. Sachdev, "A new SEC-DED error correction code subclass for adjacent MBU tolerance in embedded memory," *IEEE Trans. Device Mater. Rel.*, vol. 13, no. 1, pp. 223–230, Mar. 2013.

- [11] Z. Ming, X. L. Yi, and L. H. Wei, "New SEC-DED-DAEC codes for multiple bit upsets mitigation in memory," in *Proc. IEEE/IFIP 19th Int. Conf. VLSI-SoC*, Oct. 2011, pp. 254–259.

- [12] A. Dutta, "Low cost adjacent double error correcting code with complete elimination of miscorrection within a dispersion window for multiple bit upset tolerant memory," in *Proc. IEEE/IFIP 20th Int. Conf. VLSI SoC*, 2012, pp. 287–290.

- [13] P. Reviriego, S. Pontarelli, J. A. Maestro, and M. Ottavi, "Low-cost single error correction multiple adjacent error correction codes," *Electron. Lett.*, vol. 48, no. 23, pp. 1470–1472, Nov. 2012.

- [14] P. Reviriego, M. Flanagan, S. Liu, and J. A. Maestro, "Multiple cell upset correction in memories using difference set codes," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 11, pp. 2592–2599, Nov. 2012.

- [15] R. Datta and N. A. Touba, "Generating burst-error correcting codes from orthogonal latin square codes—A graph theoretic approach," in *Proc. IEEE Int. Symp. Defect and Fault Tolerance in VLSI and Nanotechnol. Syst.*, Oct. 2011, pp. 367–373.

- [16] M. Y. Hsiao, D. C. Bossen, and R. T. Chien, "Orthogonal Latin square codes," *IBM J. Res. Develop.*, vol. 14, no. 4, pp. 390–394, Jul. 1970.

- [17] A. R. Alameldeen, Z. Chishti, C. Wilkerson, W. Wu, and S.-L. Lu, "Adaptive cache design to enable reliable low-voltage operation," *IEEE Trans. Comput.*, vol. 60, no. 1, pp. 50–63, Jan. 2011.

- [18] S. E. Lee, Y. S. Yang, G. S. Choi, W. Wu, and R. Iyer, "Low-power, resilient interconnection with orthogonal latin squares," *IEEE Des. Test Comput.*, vol. 28, no. 2, pp. 30–39, Mar./Apr. 2011.

- [19] S. Lin and D. J. Costello, *Error Control Coding*, 2nd ed. Englewood Cliffs, NJ, USA: Prentice-Hall, 2004.

- [20] J. E. Stine *et al.*, "FreePDK: An open-source variation-aware design kit," in *Proc. IEEE Int. Conf. MSE*, Jun. 2007, pp. 173–174.